October 2006

# FAN6520A Single Synchronous Buck PWM Controller

#### **Features**

- Output Range: 0.8V to V<sub>IN</sub>

- 0.8V Internal Reference

- ±1.5% Over Line Voltage and Temperature

- Drives N-Channel MOSFETs

- Simple Single-Loop Control Design

- Voltage-Mode PWM Control

- Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Cycle

- Lossless, Programmable, Over-Current Protection

- Uses Upper MOSFET's R<sub>DS(ON)</sub>

- Small Converter Size

- 300kHz Fixed-Frequency Oscillator

- Internal Soft-Start

- 8-Lead SOIC

## **Applications**

- Power Supplies for PC Subsystems and Peripherals

- MCH, GTL, and AGP Supplies

- Cable Modems, Set-Top Boxes, and DSL Modems

- DSP, Memory

- Low-Voltage Distributed Power Supplies

## **Description**

The FAN6520A simplifies implementing a complete control and protection scheme for a DC-DC stepdown converter. Designed to drive N-channel MOSFETs in a synchro-nous buck topology, the FAN6520A integrates the control, output adjustment, monitoring, and protection functions into a single 8-lead package.

The FAN6520A employs a single feedback loop and voltage-mode control with fast transient response. The output voltage can be precisely regulated to as low as 0.8V, with a maximum tolerance of  $\pm 1.5\%$  over-temperature and line-voltage variations. A fixed-frequency oscillator reduces design complexity, while balancing typical application cost. The error amplifier features a 15MHz gainbandwidth product and an  $8V/\mu s$  slew rate, which enables high converter bandwidth for fast transient performance. The resulting PWM duty cycles range from 0% to 100%.

The IC monitors the drop across the upper MOSFET and inhibits PWM operation appropriately to protect against over-current conditions. This approach simplifies the implementation and improves efficiency by eliminating the need for a current sense resistor.

The FAN6520A is rated for operation from 0° to +70°C, with the FAN6520Al rated from -40° to +85°C.

## **Ordering Information**

| Part Number | Temperature Range | Package | Packing       |

|-------------|-------------------|---------|---------------|

| FAN6520AM   | 0°C to 70°C       | SOIC-8  | Rails         |

| FAN6520AMX  | 0°C to 70°C       | SOIC-8  | Tape and Reel |

| FAN6520AIM  | -40°C to 85°C     | SOIC-8  | Rails         |

| FAN6520AIMX | -40°C to 85°C     | SOIC-8  | Tape and Reel |

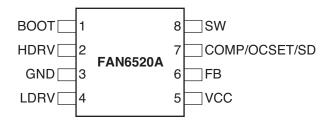

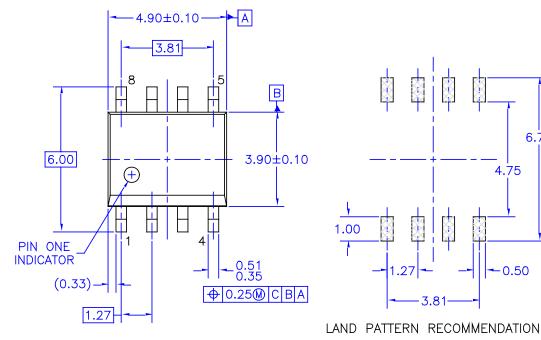

# **Pin Configuration**

FAN6520AM 8-Pin SOIC Package

## **Pin Definitions**

| Pin# | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

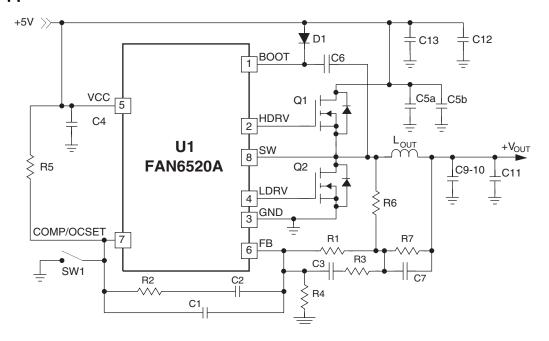

| 1    | BOOT              | <b>Bootstrap Supply Input.</b> Provides a boosted voltage to the high-side MOSFET driver. Connect to bootstrap capacitor, as shown in Figure 1.                                                                                                                                                                                                                                                                                                                                                          |

| 2    | HDRV              | <b>High-Side Gate-Drive Output.</b> Connect to the gate of the high-side power MOSFET(s). This pin is monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                                                                                                                                                                                                    |

| 3    | GND               | <b>Ground.</b> The signal and power ground for the IC. Tie this pin to the ground island/plane through the lowest impedance connection available. Connect directly to source of low-side MOSFET(s).                                                                                                                                                                                                                                                                                                      |

| 4    | LDRV              | <b>Low-Side Gate-Drive Output.</b> Connect to the gate of the low-side power MOSFET(s). This pin is monitored by the adaptive shoot-through protection circuitry to determine when the lower MOSFET has turned off.                                                                                                                                                                                                                                                                                      |

| 5    | VCC               | <b>VCC.</b> Provides bias power to the IC and the drive voltage for LDRV. Bypass with a ceramic capacitor as close to this pin as possible.                                                                                                                                                                                                                                                                                                                                                              |

| 6    | FB                | <b>Feedback.</b> This pin is the inverting input of the internal error amplifier. Use this pin, in combination with the COMP/OCSET pin, to compensate the voltage-control feedback loop of the converter.                                                                                                                                                                                                                                                                                                |

| 7    | COMP/<br>OCSET/SD | Compensation / Over-Current Set Point / Shut Down. This is a multiplexed pin. During operation, the output of the error amplifier drives this pin. During a short period of time following power-on reset (POR), this pin is used to determine the over-current threshold of the converter. Pulling COMP/OCSET to a level below 0.8V disables the controller. Disabling the controller causes the oscillator to stop, the HDRV and LDRV outputs to be held low, and the soft-start circuitry to restart. |

| 8    | SW                | <b>Switch Node Input.</b> The SW pin provides return for the high-side bootstrapped driver, is a sense point for the adaptive shoot-through protection, and is used to monitor the drop across the upper MOSFET's R <sub>DS(ON)</sub> for current limit. Connect as shown in Figure 1.                                                                                                                                                                                                                   |

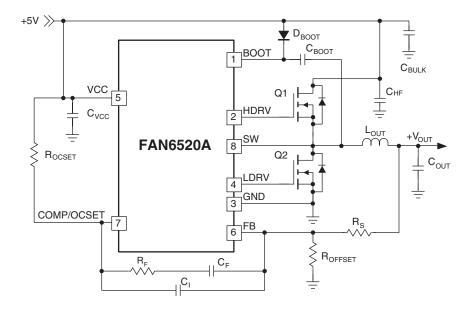

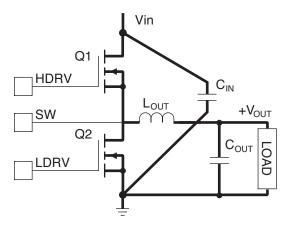

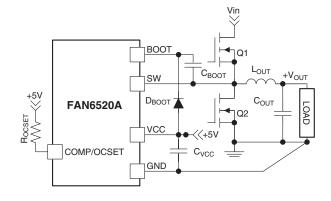

# **Typical Application**

Figure 1. Typical Application

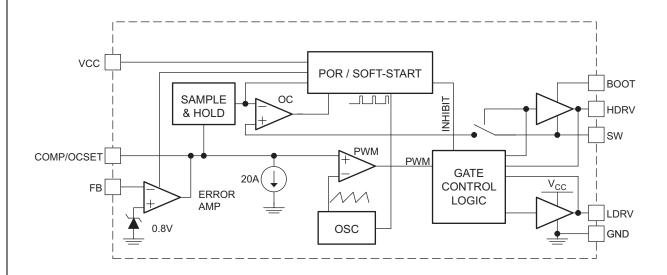

Figure 2. Functional Block Diagram

## **Absolute Maximum Ratings**

The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table defines the conditions for actual device operation.

| Parameter                                   |                                   | Min. | Max. | Units |

|---------------------------------------------|-----------------------------------|------|------|-------|

| VCC to GND                                  |                                   |      | 6    | V     |

| VBOOT to GND                                | )                                 |      | 15   | V     |

| HDRV (V <sub>BOOT</sub> – V <sub>SW</sub> ) |                                   |      | 6    | V     |

| LDRV                                        |                                   | -0.5 | 6    | V     |

| SW to PGND                                  | Continuous                        | -0.5 | 6    | V     |

|                                             | Transient ( t < 50ns, F < 500kHz) | -3   | 7    | V     |

| All other pins                              |                                   |      | 5.5  | V     |

## **Thermal Information**

| Symbol           | Parameter                                | Min. | Тур. | Max. | Units |

|------------------|------------------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage Temperature                      | -65  |      | 150  | °C    |

| TL               | Lead Soldering Temperature, 10 seconds   |      |      | 300  | °C    |

|                  | Vapor Phase, 60 seconds                  |      |      | 215  | °C    |

|                  | Infrared, 15 seconds                     |      |      | 220  | °C    |

| P <sub>D</sub>   | Power Dissipation, T <sub>A</sub> = 25°C |      |      | 715  | mW    |

| Θ <sub>JC</sub>  | Thermal Resistance, Junction-to-Case     |      | 40   |      | °C/W  |

| $\Theta_{JA}$    | Thermal Resistance, Junction-to-Ambient  |      | 140  |      | °C/W  |

# **Recommended Operating Conditions**

| Symbol          | Parameter            | Conditions  | Min. | Тур. | Max. | Units |

|-----------------|----------------------|-------------|------|------|------|-------|

| V <sub>CC</sub> | Supply Voltage       | VCC to PGND | 4.5  | 5    | 5.5  | V     |

| т               | Ambient Temperature  | FAN6520A    | 0    |      | 70   | °C    |

| T <sub>A</sub>  | Ambient Temperature  | FAN6520AI   | -40  |      | 85   | °C    |

| T <sub>J</sub>  | Junction Temperature |             | -40  |      | 125  | °C    |

# **Electrical Specifications**

$V_{CC}$  = 5V and  $T_A$  = 25°C, using the circuit shown in Figure 1 unless otherwise noted. The • denotes specifications that apply over the full operating temperature range.

| Symbol               | Parameter                    | Conditions                 |   | Min. | Тур. | Max. | Units |

|----------------------|------------------------------|----------------------------|---|------|------|------|-------|

| Supply Cu            | ırrent                       |                            |   |      | •    | •    | •     |

| I <sub>VCC</sub>     | V <sub>CC</sub> Current      | HDRV, LDRV open            | • | 1.5  | 2.4  | 3.8  | mA    |

| Power-On             | Reset                        |                            |   |      | •    | •    | •     |

| POR                  | Rising VCC POR Threshold     |                            | • | 4.00 | 4.22 | 4.45 | V     |

|                      | VCC POR Threshold Hysteresis |                            |   |      | 170  |      | mV    |

| Oscillator           |                              |                            |   |      | •    |      |       |

| Fosc                 | Frequency                    | FAN6520A                   | • | 250  | 300  | 340  | kHz   |

|                      |                              | FAN6520AI                  | • | 230  | 300  | 340  | kHz   |

| ΔV <sub>OSC</sub>    | Ramp Amplitude               |                            | • |      | 1.5  |      | Vp-p  |

| Reference            | •                            |                            |   |      | •    |      |       |

| V <sub>REF</sub>     | Reference Voltage            | T <sub>A</sub> = 0 to 70°C | • | 788  | 800  | 812  | mV    |

|                      |                              | FAN6520AI                  | • | 780  | 800  | 820  | mV    |

| Error Amp            | olifier                      |                            |   |      | •    |      |       |

|                      | DC Gain                      |                            |   |      | 88   |      | dB    |

| GBWP                 | Gain – Bandwidth Product     |                            |   |      | 15   |      | MHz   |

| S/R                  | Slew Rate                    |                            |   |      | 8    |      | V/µs  |

| Gate Drive           | ers                          | •                          |   |      |      |      |       |

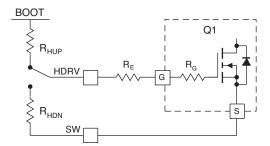

| R <sub>HUP</sub>     | HDRV PullI-Up Resistance     |                            |   |      | 2.5  |      | Ω     |

| R <sub>HDN</sub>     | HDRV Pull-Down Resistance    |                            |   |      | 2.0  |      | Ω     |

| R <sub>LUP</sub>     | LDRV Pull-Up Resistance      |                            |   |      | 2.5  |      | Ω     |

| R <sub>LDN</sub>     | LDRV Pull-Down Resistance    |                            |   |      | 1.0  |      | Ω     |

| Protection           | n/Disable                    | •                          | • |      | •    | •    | •     |

| I <sub>OCSET</sub>   | OCSET Current Source         | FAN6520A                   | • | 17   | 20   | 22   | μΑ    |

|                      |                              | FAN6520AI                  | • | 14   | 20   | 24   | μΑ    |

| V <sub>DISABLE</sub> | Disable Threshold            |                            |   |      | 800  |      | mV    |

#### Notes:

- 1. All limits at operating temperature extremes are guaranteed by design, characterization, and statistical quality control.

- 2. AC specifications guaranteed by design/characterization (not production tested).

## **Circuit Description**

#### Initialization

The FAN6520A automatically initializes upon receipt of power. The Power-On Reset (POR) function continually monitors the bias voltage at the VCC pin. When the supply voltage exceeds its POR threshold, the IC initiates the Over-Current Protection (OCP) sample-and-hold operation. Upon completion of the OCP sample-and-hold operation, the POR function initiates soft-start operation.

## **Over-Current Protection**

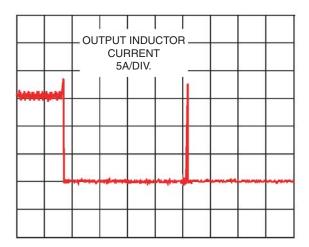

The over-current function protects the converter from a shorted output by using the upper MOSFET's on-resistance, R<sub>DS(ON)</sub>, to monitor the current. This method enhances the converter's efficiency and reduces cost by eliminating the need for a current-sensing resistor. The over-current function cycles the soft-start function in a hiccup mode to provide fault protection. A resistor (ROC-SET) programs the over-current trip level (see Typical Application diagram). Immediately following POR, the FAN6520A initiates the Over-Current Protection sampling-and-hold operation. First, the internal error amplifier is disabled. This allows an internal 20µA current sink to develop a voltage across R<sub>OCSET</sub>. The FAN6520A then samples this voltage at the COMP pin. This sampled voltage, which is referenced to the VCC pin, is held internally as the over-current set point. When the voltage across the upper MOSFET, which is also referenced to the VCC pin, exceeds the over-current set point, the over-current function initiates a soft-start sequence. Figure 3 shows the inductor current after a fault is introduced while running at 15A. The continuous fault causes the FAN6520A to go into a hiccup mode with a typical period of 25ms. The inductor current increases to 18A during the soft-start interval and causes an over-current trip. The converter dissipates very little power with this method. The measured input power for the conditions shown in Figure 3 is 1.5W.

**Figure 3. Over-Current Operation**

The over-current function trips at a peak inductor current  $(I_{PEAK})$  determined by:

$$I_{PEAK} = \frac{I_{OCSET} \times R_{OCSET}}{R_{DS(ON)}}$$

(1)

where  $I_{OCSET}$  is the internal OCSET current source (20µA typical). The OC trip point varies mainly due to the MOSFET's  $R_{DS(ON)}$  variations. To avoid over-current tripping in the normal operating load range, find the  $R_{OCSET}$  resistor from the equation above with:

- The maximum R<sub>DS(ON)</sub> at the highest junction temperature

- The minimum I<sub>OCSFT</sub> from the specification table

- Determine  $I_{PEAK}$  for  $I_{PEAK} > I_{OUT(MAX)} + \frac{\Delta I}{2}$  where  $\Delta I$  is the output inductor ripple current.

For an equation for the ripple current, see "Output Inductor  $(L_{out})$ " under Component Selection.

Internal circuitry of the FAN6520A does not recognize a voltage drop across  $R_{OCSET}$  larger than 0.5V. Any voltage drop across  $R_{OCSET}$  greater than 0.5V sets the overcurrent trip point to:

$$I_{PEAK} = \frac{0.5V}{R_{DS(ON)}}$$

(2)

An over-current trip cycles the soft-start function.

#### **Soft-Start**

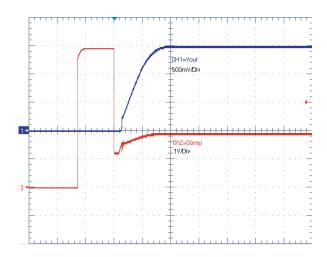

The POR function initiates the soft-start sequence after the over-current set point has been sampled. Soft-start clamps the error amplifier output (COMP pin) and reference input (noninverting terminal of the error amp) to the internally generated soft-start voltage. Figure 4 shows a typical start-up interval where the COMP/OCSET pin has been released from a grounded (system shutdown) state. Initially, the COMP/OCSET is used to sample the over-current set point by disabling the error amplifier and drawing  $20\mu A$  through  $R_{\mbox{\scriptsize OCSET}}$ . Once the over-current level has been sampled, the soft-start function is initiated. The clamp on the error amplifier (COMP/OCSET pin) initially controls the converter's output voltage during soft-start. The oscillator's triangular waveform is compared to the ramping error amplifier voltage. This generates SW pulses of increasing width that charge the output capacitor(s). When the internally generated softstart voltage exceeds the feedback (FB pin) voltage, the output voltage is in regulation. This method provides a rapid and controlled output voltage rise. The entire startup sequence typically takes about 11ms.

Figure 4. Soft-Start Interval

The FAN6520A incorporates a MOSFET shoot-through protection method that allows a converter to both sink and source current. Care should be exercised when designing a converter with the FAN6520A when it is known that the converter may sink current.

When the converter is sinking current, it is behaving as a boost converter regulating its input voltage. This means that the converter is boosting current into the  $V_{CC}$  rail, which supplies the bias voltage to the FAN6520A. If this current has nowhere to go—such as to other distributed loads on the  $V_{CC}$  rail, through a voltage limiting protection device, or other methods—the capacitance on the  $V_{CC}$  bus absorbs the current. This allows the voltage level of the  $V_{CC}$  rail to increase. If the voltage level of the rail is boosted to a level that exceeds the maximum voltage rating of the FAN6520A, the IC experiences an irreversible failure and the converter is no longer operational. Ensure that there is a path for the current to follow, other than the capacitance on the rail, to prevent this failure mode.

# **Application Information**

## **Layout Considerations**

In any high-frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. Use wide, short-printed traces to minimize interconnecting impedances. The critical components should be located as close together as possible, using ground plane construction or single-point grounding.

Figure 5. Printed Circuit Board Power and Ground Planes or Islands

Figure 5 shows the critical power components of the converter. To minimize voltage overshoot, the interconnecting wires (indicated by heavy lines) should be part of a ground or power plane in a printed circuit board. The components shown in Figure 5 should be located as close together as possible. Note that the capacitors  $C_{\rm IN}$  and  $C_{\rm OUT}$  may each represent numerous physical capacitors. Locate the FAN6520A within two inches of the Q1 and Q2 MOSFETs. The circuit traces for the MOSFETs' gate and source connections from the FAN6520A must be sized to handle up to 1A peak current.

Figure 5 shows the circuit traces that require additional layout consideration. Use single point and ground plane construction for the circuits shown. Minimize any leakage current paths on the COMP/OCSET pin and locate the resistor,  $R_{\mbox{\scriptsize OSCET}}$ , close to the COMP/OCSET pin because the internal current source is only 20µA. Provide local  $V_{\mbox{\scriptsize CC}}$  decoupling between the VCC and GND pins. Locate the capacitor, CBOOT, as close as practical to the BOOT and PHASE pins. All components used for feedback compensation should be located as close to the IC as practical.

Figure 6. PCB Small Signal Layout Guidelines

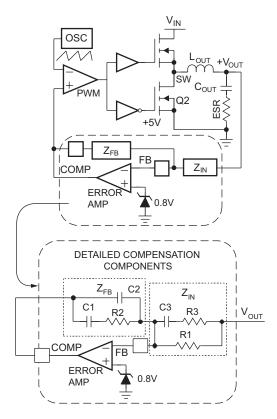

## Feedback Compensation

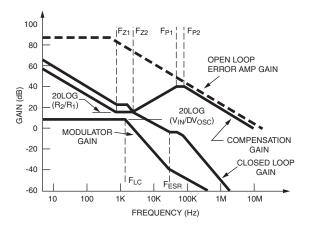

Figure 7 highlights the voltage-mode control loop for a synchronous-rectified buck converter. The output voltage ( $V_{OUT}$ ) is regulated to the reference voltage level. The error amplifier (Error Amp) output ( $V_{E/A}$ ) is compared with the oscillator (OSC) triangular wave to provide a pulse-width modulated (PWM) wave with an amplitude of  $V_{IN}$  at the SW node. The PWM wave is smoothed by the output LC filter ( $L_{OUT}$  and  $C_{OUT}$ ).

Figure 7. Voltage Mode Buck Converter Compensation Design

The modulator transfer function is the small-signal transfer function of  $V_{OUT}/V_{COMP}$ . This function is dominated by a DC gain and the output filter (L\_OUT and C\_OUT), with a double-pole break frequency at  $F_{LC}$  and a zero at  $F_{ESR}.$  The DC gain of the modulator is the input voltage (V\_IN) divided by the peak-to-peak oscillator voltage ( $\Delta V_{OSC}.$ )

The following equations define the modulator break frequencies as a function of the output LC filter:

$$F_{LC} = \frac{1}{2\pi\sqrt{L \times C}}$$

(3)

$$F_{ESR} = \frac{1}{2\pi \times ESR \times C}$$

(4)

The compensation network consists of the error amplifier (internal to the FAN6520A) and the impedance networks  $Z_{IN}$  and  $Z_{FB}$ . The goal of the compensation network is to provide a closed-loop transfer function with the highest 0dB crossing frequency ( $F_{0dB}$ ) and adequate phase margin. Phase margin is the difference between the closed-loop phase at  $F_{0dB}$  and 180 degrees. The equations below relate the compensation network's poles, zeros, and gain to the components (R1, R2, R3, C1, C2, and C3), shown in Figure 7.

$$F_{Z1} = \frac{1}{2\pi R_2 C_1} \tag{5}$$

$$F_{P1} = \frac{1}{2\pi R_2 \left(\frac{C_1 C_2}{C_1 + C_2}\right)}$$

(6)

$$F_{Z2} = \frac{1}{2\pi C_3 (R_1 + R_3)} \tag{7}$$

$$F_{P2} = \frac{1}{2\pi R_3 C_3} \tag{8}$$

Use the following steps to locate the poles and zeros of the compensation network:

- Pick gain (R2/R1) for the desired converter bandwidth.

- Place the first zero below the filter's double pole (~75% F<sub>LC</sub>).

- 3. Place the second zero at filter's double pole.

- 4. Place the first pole at the ESR zero.

- Place the second pole at half the switching frequency.

- 6. Check the gain against the error amplifier's open-loop gain.

- 7. Estimate phase margin. Repeat if necessary.

Figure 8 shows an asymptotic plot of the DC-DC converter's gain vs. frequency. The actual modulator gain has a high gain peak due to the high Q factor of the output filter and is not shown in Figure 8. Using the above guidelines should give a compensation gain similar to the curve plotted. The open-loop error amplifier gain bounds the compensation gain. Check the compensation gain at FP2 with the capabilities of the error amplifier. The closed-loop gain is constructed on the graph of Figure 8 by adding the modulator gain (in dB) to the compensation gain (in dB). This is equivalent to multiplying the modulator transfer function by the compensation transfer function and plotting the gain.

The compensation gain uses external impedance networks  $Z_{FB}$  and  $Z_{IN}$  to provide a stable high bandwidth overall loop. A stable control loop has a gain crossing with a -20dB/decade slope and a phase margin greater than 45°. Include worst-case component variations when determining phase margin.

Figure 8. Asymptotic Bode Plot of Converter Gain

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout.

## **Component Selection**

## **Output Capacitors (COUT)**

Modern components and loads are capable of producing transient load rates above 1A/ns. High-frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. Effective Series Resistance (ESR) and voltage rating are typically the prime considerations for the bulk filter capacitors, rather than actual capacitance requirements. High-frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the performance of these low-inductance components. Consult with the load manufacturer on specific decoupling requirements. Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR determines the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes; however, the Equivalent Series Inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Since ESL is not a specified parameter, work with the capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component. Generally, multiple small-case electrolytic capacitors perform better than a single large-case capacitor.

## Output Inductor (L<sub>OUT</sub>)

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage ( $\Delta V$ ) and current ( $\Delta I$ ) are approximated by the following equations:

$$\Delta I = \left(\frac{V_{IN} - V_{OUT}}{F_{SW} \times L}\right) \times \frac{V_{OUT}}{V_{IN}} \qquad \Delta V \approx ESR \times \Delta I \tag{9}$$

Increasing the inductance value reduces the ripple current and voltage, but also reduces the converter's ability to quickly respond to a load transient. One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control-loop design, the FAN6520A provides either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval, the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

Depending on whether there is a load application or a load removal, the response time to a load transient (I<sub>STEP</sub>) is different. The following equations give the approximate response time interval for application and removal of a transient load:

$$T_{RISE} = \frac{L \times I_{STEP}}{V_{IN} - V_{OUT}}$$

(10)

$$T_{\text{FALL}} = \frac{L \times I_{\text{STEP}}}{V_{\text{OUT}}} \tag{11}$$

where  $T_{RISE}$  is the response time to the application of a positive  $I_{STEP}$  and  $T_{FALL}$  is the response time to a load removal (negative  $I_{STEP}$ ). The worst-case response time can be either at application or removal of load. Check both of these equations at the minimum and maximum output levels for the worst-case response time.

#### **Input Capacitor Selection**

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high-frequency decoupling and bulk capacitors to supply the current needed each time Q1 turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of Q1 and the source of Q2. The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and the largest RMS current required by the circuit. The capacitor voltage rating should be at least

1.25 times greater than the maximum input voltage. A voltage rating of 1.5 times is a conservative guideline.

The RMS current rating requirement (I<sub>RMS</sub>) for the input capacitor of a buck regulator is:

$$I_{RMS} = I_{L} \sqrt{(D - D^{2})}$$

where the converter duty cycle is  $D = \frac{V_{OUT}}{V_{IN}}$ . (12)

For a through-hole design, several electrolytic capacitors may be needed. For surface-mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor's surge current rating. The capacitors must be capable of handling the surge current at power-up. Some capacitor series available from reputable manufacturers are surge current tested.

## **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor  $(C_{BOOT})$  and the internal diode, as shown in Figure 1. Select these components after the high-side MOSFET has been chosen. The required capacitance is determined using the following equation:

$$C_{BOOT} = \frac{Q_{G}}{\Delta V_{BOOT}}$$

(13)

where  $Q_G$  is the total gate charge of the high-side MOS-FET and  $\Delta V_{BOOT}$  is the voltage droop allowed on the high-side MOSFET drive. To prevent loss of gate drive, the bootstrap capacitance should be at least 50 times greater than the  $C_{ISS}$  of Q1.

#### **Thermal Considerations**

Total device dissipation:

$$P_D = P_O + P_{HDRV} + P_{LDRV}$$

(14)

where P<sub>O</sub> represents quiescent power dissipation.

$$P_Q = V_{CC} \times [4mA + 0.036 (F_{SW} - 100)]$$

(15)

where F<sub>SW</sub> is switching frequency (in kHz).

$\mathsf{P}_{\mbox{\scriptsize HDRV}}$  represents internal power dissipation of the upper FET driver.

$$P_{HDRV} = P_{H(R)} \times P_{H(F)} \tag{16}$$

where  $P_{H(R)}$  and  $P_{H(F)}$  are internal dissipations for the rising and falling edges respectively.

$$P_{H(R)} = P_{Q1} \times \frac{R_{HUP}}{R_{HUP} + R_E + R_G}$$

(17)

$$P_{H(F)} = P_{Q1} \times \frac{R_{HDN}}{R_{HDN} + R_E + R_G}$$

(18)

where:

$$P_{Q1} = Q_{G1} \times V_{GS(Q1)} \times F_{SW}$$

(19)

where Q<sub>G1</sub> is total gate charge of Q1 for its applied V<sub>GS</sub>.

As described in the equations above, the total power consumed in driving the gate is divided in proportion to the resistances in series with the MOSFET's internal gate node, as shown in Figure 9.

Figure 9. Driver Dissipation Model

R<sub>G</sub> is the polysilicon gate resistance internal to the FET. R<sub>E</sub> is the external gate drive resistor implemented in many designs. Note that the introduction of R<sub>E</sub> can reduce driver power dissipation, but excess R<sub>E</sub> may cause errors in the "adaptive gate drive" circuitry. For more information, please refer to Application Note *AN-6003, "Shoot-through" in Synchronous Buck Converters at* http://www.fairchildsemi.com/an/AN/AN-6006.pdf.

P<sub>LDRV</sub> is dissipation of the lower FET driver.

$$P_{LDRV} = P_{L(R)} \times P_{L(F)} \tag{20}$$

where  $P_{H(R)}$  and  $P_{H(F)}$  are internal dissipations for the rising and falling edges, respectively:

$$P_{L(R)} = P_{Q2} \times \frac{R_{LUP}}{R_{LUP} + R_E + R_G}$$

(21)

$$P_{L(F)} = P_{Q2} \times \frac{R_{LDN}}{R_{HDN} + R_{F} + R_{G}}$$

(22)

where:

$$P_{Q2} = Q_{G2} \times V_{GS(Q2)} \times F_{SW}. \tag{23}$$

#### Power MOSFET Selection

For more information on MOSFET selection for synchronous buck regulators, refer to: *AN-6005: Synchronous Buck MOSFET Loss Calculations at* <a href="http://www.fairchild-semi.com/an/AN/AN-6005.pdf">http://www.fairchild-semi.com/an/AN/AN-6005.pdf</a>.

Losses in a MOSFET are the sum of its switching ( $P_{SW}$ ) and conduction ( $P_{COND}$ ) losses.

In typical applications, the FAN6520A converter's output voltage is low with respect to its input voltage; therefore the lower MOSFET (Q2) is conducting the full load current for most of the cycle. Choose a MOSFET for Q2 that has low  $R_{DS(ON)}$  to minimize conduction losses.

In contrast, the high-side MOSFET (Q1) has a much shorter duty cycle and its conduction loss has less impact. Q1, however, sees most of the switching losses, so Q1's primary selection criteria should be gate charge.

### **High-Side Losses**

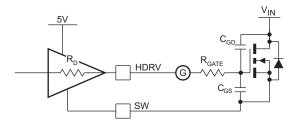

Figure 10 shows a MOSFET's switching interval, with the upper graph being the voltage and current on the drainto-source and the lower graph detailing  $V_{GS}$  vs. time with a constant current charging the gate. The x-axis, therefore, is also representative of gate charge  $(Q_G)$ .  $C_{ISS} = C_{GD} + C_{GS}$  and it controls t1, t2, and t4 timing.  $C_{GD}$  receives the current from the gate driver during t3 (as  $V_{DS}$  is falling). The gate charge  $(Q_G)$  parameters on the lower graph are either specified or can be derived from the MOSFET's datasheet.

Assuming switching losses are about the same for both the rising edge and falling edge, Q1's switching losses occur during the shaded time when the MOSFET has voltage across it and current through it.

These losses are given by:

$$P_{UPPER} = P_{SW} + P_{COND}$$

(24)

$$P_{SW} = \left(\frac{V_{DS} \times I_{L}}{2} \times 2 \times t_{s}\right) F_{SW}$$

(25)

$$P_{COND} = \left(\frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT}^{2} \times R_{DS(ON)}$$

(26)

where  $P_{UPPER}$  is the upper MOSFET's total losses,  $P_{SW}$  and  $P_{COND}$  are the switching and conduction losses for a given MOSFET,  $R_{DS(ON)}$  is at the maximum junction temperature ( $T_J$ ), and  $t_S$  is the switching period (rise or fall time) and is t2+t3 (Figure 10).

The driver's impedance and  $C_{ISS}$  determine t2, while t3's period is controlled by the driver's impedance and  $Q_{GD}$ . Since most of  $t_S$  occurs when  $V_{GS} = V_{SP}$ , use a constant current assumption for the driver to simplify the calculation of  $t_S$ :

$$t_{S} \approx \frac{Q_{G(SW)}}{I_{DRIVER}} \approx \frac{Q_{G(SW)}}{\left(\frac{V_{CC} - V_{SP}}{R_{DRIVER} + R_{GATE}}\right)}$$

(27)

Figure 10. Switching Losses and Q<sub>G</sub>

Figure 11. Drive Equivalent Circuit

Most MOSFET vendors specify  $Q_{GD}$  and  $Q_{GS}$ .  $Q_{G(SW)}$  can be determined as  $Q_{G(SW)} = Q_{GD} + Q_{GS} - Q_{TH}$  where  $Q_{TH}$  is the gate charge required to reach the MOSFET threshold ( $V_{TH}$ ). For the high-side MOSFET,  $V_{DS} = V_{IN}$ , which can be as high as 20V in a typical portable application. Care should be taken to include the delivery of the MOSFET's gate power ( $P_{GATE}$ ) in calculating the power dissipation required:

$$P_{GATE} = Q_G \times V_{CC} \times F_{SW}$$

(28)

where Q<sub>G</sub> is the total gate charge to reach V<sub>CC</sub>.

#### **Low-Side Losses**

Q2, however, switches on or off with its parallel Shottky diode conducting, therefore  $V_{DS}$  Ý 0.5V. Since  $P_{SW}$  is proportional to V<sub>DS</sub>, Q2's switching losses are negligible and Q2 can be selected based on  $R_{DS(ON)}$  only.

Conduction losses for Q2 are given by:

$$P_{COND} = (1-D) \times I_{OUT}^2 \times R_{DS(ON)}$$

(29)

where  $R_{\text{DS}(\text{ON})}$  is the  $R_{\text{DS}(\text{ON})}$  of the MOSFET at the highest operating junction temperature and

$$D = \frac{V_{OUT}}{V_{IN}}$$

is the minimum duty cycle for the converter. Since  $D_{MIN} < 20\%$  for portable computers, (1-D)  $\approx 1$  pro-

duces a conservative result, simplifying the calculation.

The maximum power dissipation (P<sub>D(MAX)</sub>) is a function of the maximum allowable die temperature of the lowside MOSFET, the  $\theta_{\mbox{\scriptsize J-A}},$  and the maximum allowable ambient temperature rise:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{J-A}}$$

(30)

depends primarily on the amount of PCB area that can be devoted to heat sinking. Refer to Fairchild Application Note AN-1029 Maximum Power Enhancement Techniques for SO-8 Power MOSFETs at http://www.fairchildsemi.com/an/AN/AN-1029.pdf.

# **Typical Application Circuit**

Figure 12. 5V to 1.5V 15A DC-DC Converter

# **Evaluation Board Bill of Materials (1.5V, 15 Amps):**

| Ref Des       | Description                  | Manufacturer        | P/N                 | Qty |

|---------------|------------------------------|---------------------|---------------------|-----|

| C1            | 100pF Capacitor, 603         | Any                 |                     | 1   |

| C2            | 0.01µF Capacitor, 603        | Any                 |                     | 1   |

| C3            | Not Populated                |                     |                     | 0   |

| C4            | 0.1µF Capacitor, 603         | Any                 |                     | 1   |

| C5A,C5B       | 1μF Capacitor, 805           | Any                 |                     | 3   |

| C6,C11        | 0.1µF Capacitor, 603         | Any                 |                     | 2   |

| C7            | Not Populated Capacitor, 603 | Any                 |                     | 0   |

| C9-10,C12,C13 | 1500µF Capacitor, 6.3V       | United<br>Chemi-con | KZJ6.3VB152M10X12LL | 4   |

| D1            | Diode, 30mA, 30V             | Fairchild           | MMSD4148            | 1   |

| L1            | 1.2µH Inductor               | InterTechnical      | SC5015-1R2M         | 1   |

| Q1,Q2         | MOSFET                       | Fairchild           | FDD6606             | 2   |

| R1            | 2.2kΩ 1% Resistor, 603       | Any                 |                     | 1   |

| R2            | 30.1kΩ 1% Resistor, 603      | Any                 |                     | 1   |

| R3            | Not Populated                |                     |                     | 0   |

| R4            | 2.49kΩ Resistor, 603         | Any                 |                     | 1   |

| R5            | 11.8kΩ Resistor, 603         | Any                 |                     | 1   |

| R6            | Not Populated Resistor, 603  | Any                 |                     | 0   |

| R7            | 0Ω Resistor, 603             | Any                 |                     | 1   |

| PB1           | Pushbutton, miniature        | Digikey             | P8007S-ND           | 1   |

| U1            | Single Synchronous Buck PWM  | Fairchild           | FAN6520A            | 1   |

| TP1,2,3,4     | Test Points                  | KeyStone            | 1514-2              | 4   |

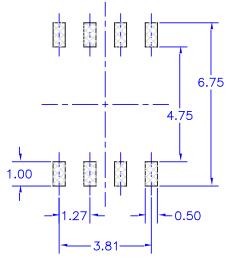

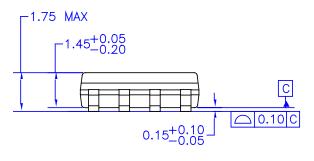

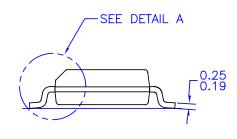

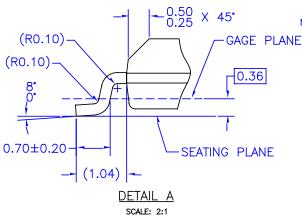

# **Dimensional Outline Drawing**

- NOTES: UNLESS OTHERWISE SPECIFIED

- THIS PACKAGE CONFORMS TO JEDEC MS-012, VARIATION AA, ISSUE C, DATED MAY 1990.

ALL DIMENSIONS ARE IN MILLIMETERS.

- DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS.

- STANDARD LEAD FINISH:

200 MICROINCHES / 5.08 MICRONS MIN.

LEAD/TIN (SOLDER) ON COPPER.

Figure 13. 8-Lead SOIC Package Drawing

M08AREVK

UniFET™ UltraFET® VCX™ Wire™

### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

| ACEx™                                | FACT Quiet Series™  | $OCX^{TM}$               | SILENT SWITCHER®       |  |

|--------------------------------------|---------------------|--------------------------|------------------------|--|

| ActiveArray™                         | GlobalOptoisolator™ | OCXPro™                  | SMART START™           |  |

| Bottomless™                          | GTO™                | OPTOLOGIC <sup>®</sup>   | SPM™                   |  |

| Build it Now™                        | HiSeC™              | OPTOPLANAR™              | Stealth™               |  |

| CoolFET™                             | I <sup>2</sup> C™   | PACMAN™                  | SuperFET™              |  |

| $CROSSVOLT^{\text{TM}}$              | i-Lo™               | POP™                     | SuperSOT™-3            |  |

| DOME™                                | ImpliedDisconnect™  | Power247™                | SuperSOT™-6            |  |

| EcoSPARK™                            | IntelliMAX™         | PowerEdge™               | SuperSOT™-8            |  |

| E <sup>2</sup> CMOS™                 | ISOPLANAR™          | PowerSaver™              | SyncFET™               |  |

| EnSigna™                             | LittleFET™          | PowerTrench <sup>®</sup> | TCM™                   |  |

| FACT™                                | MICROCOUPLER™       | QFET <sup>®</sup>        | TinyBoost™             |  |

| FAST <sup>®</sup>                    | MicroFET™           | QS™                      | TinyBuck™              |  |

| FASTr™                               | MicroPak™           | QT Optoelectronics™      | TinyPWM™               |  |

| FPS™                                 | MICROWIRE™          | Quiet Series™            | TinyPower™             |  |

| FRFET™                               | MSX™                | RapidConfigure™          | TinyLogic <sup>®</sup> |  |

|                                      | MSXPro™             | RapidConnect™            | TINYOPTO™              |  |

| Across the board. Around the world.™ |                     | μSerDes™                 | TruTranslation™        |  |

| The Power Franchise®                 |                     | ScalarPump™              | UHC™                   |  |

| Programmable Active Droop™           |                     |                          |                        |  |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## PRODUCT STATUS DEFINITIONS

## **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                                   |

|--------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                           |

| Preliminary              | First Production       | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                       |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                          |

Rev. I20